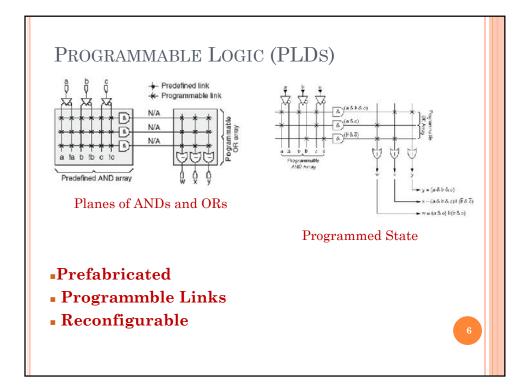

A PLD consists of an array of AND gates and an array of OR gates

Each input feeds both a non-inverting buffer and an inverting

buffer to produce the true and inverted forms of each variable.

(i.e. the input lines to the AND-gate array)

The AND outputs are called the product lines

Each product line is connected to one of the inputs of each OR

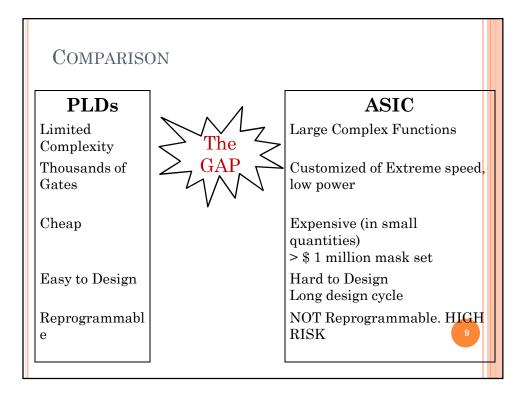

| Compariso             | DN                     |                                           |

|-----------------------|------------------------|-------------------------------------------|

| PLDs                  | ST XILINX              | ASIC                                      |

| Limited<br>Complexity | FPGA                   | Large Complex Functions                   |

| Thousands of Gates    | arge Complex Functions | Customized of Extreme<br>speed, low power |

| Cheap                 | Inexpensive            | Expensive (in small<br>quantities)        |

|                       | Easy to Design         | > \$ 1 million mask set                   |

| Easy to Design        | Reprogrammable         | Hard to Design<br>Long design cycle       |

| Reprogrammabl<br>e    |                        | NOT Reprogrammable<br>HIGH RISK           |

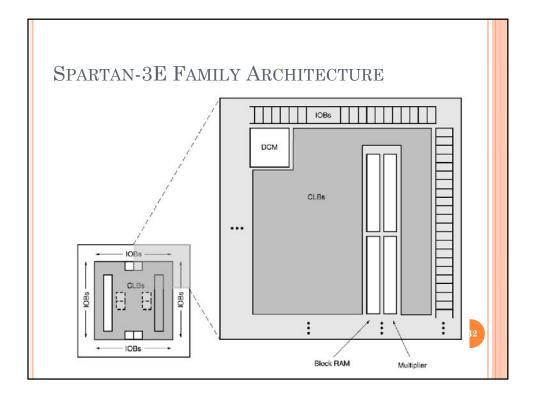

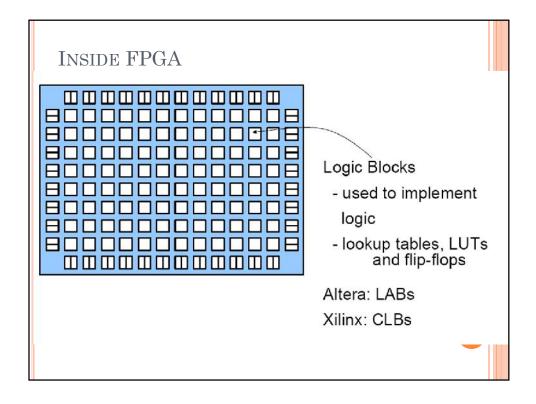

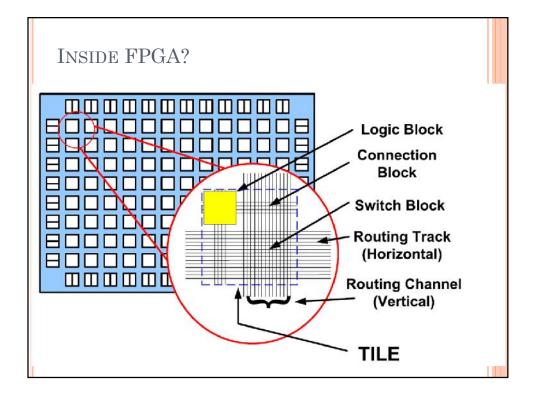

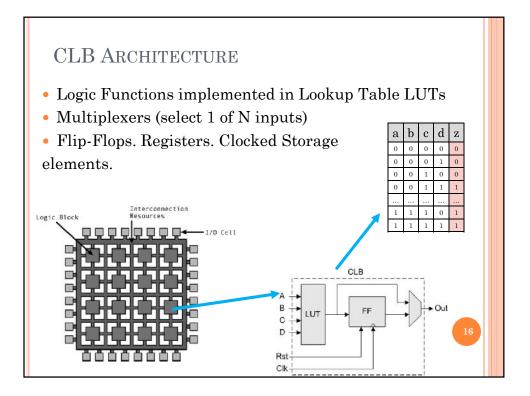

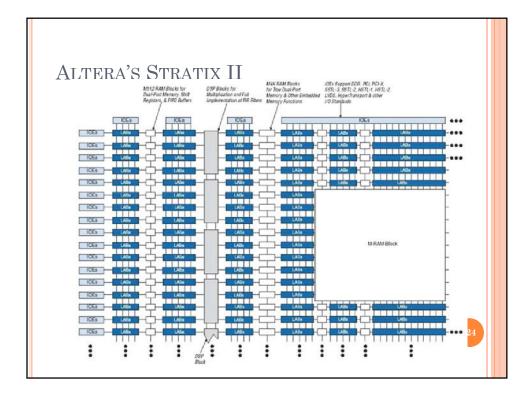

| • | Configurable Logic Blocks (CLBs) contain flexible<br>Look-Up Tables (LUTs) that implement logic plus<br>storage elements used as flip-flops or latches. CLBs<br>perform a wide variety of logical functions as well as<br>store data.                                                                                                             |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Input/Output Blocks (IOBs) control the flow of data<br>between the I/O pins and the internal logic of the<br>device. Each IOB supports bidirectional data flow plus<br>3-state operation. Supports a variety of signal<br>standards, including four high-performance differential<br>standards. Double Data-Rate (DDR) registers are<br>included. |

| • | Block RAM provides data storage in the form of<br>18-Kbit dual-port blocks.                                                                                                                                                                                                                                                                       |

| • | Multiplier Blocks accept two 18-bit binary numbers as<br>inputs and calculate the product.                                                                                                                                                                                                                                                        |

| • | Digital Clock Manager (DCM) Blocks provide<br>self-calibrating, fully digital solutions for distributing,<br>delaying, multiplying, dividing, and phase-shifting clock<br>signals.                                                                                                                                                                |

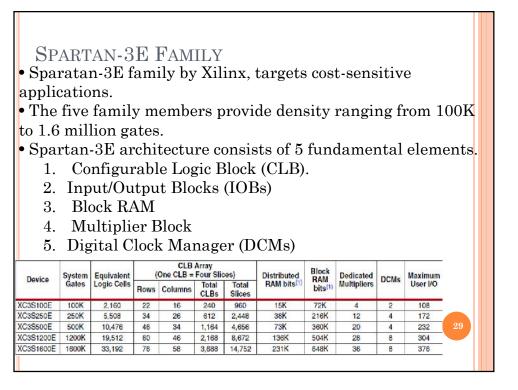

These elements are organized in the following manner.

- A ring of IOBs surrounds a regular array of CLBs.

- Each device has two columns of block RAM except for the XC3S100E, which has one column.

- Each RAM column consists of several 18-Kbit RAM blocks.

- Each block RAM is associated with a dedicated multiplier.

- The DCMs are positioned in the center with two at the top and two at the bottom of the device.

- ${\color{black}\circ}$  The XC3S100E has only one DCM at the top and bottom

- The XC3S1200E and XC3S1600E add two DCMs in the middle of the left and right sides.

The Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch<sup>31</sup> matrix that permits multiple connections to the routing.