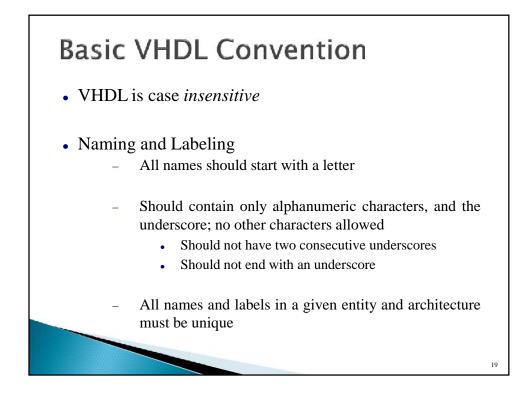

# **Basic VHDL Convention**

- Free format language

- i.e. allows spacing for readability

- Comments start with "--" and end at end of line

- Use one file per entity

- File names and entity names should match

20

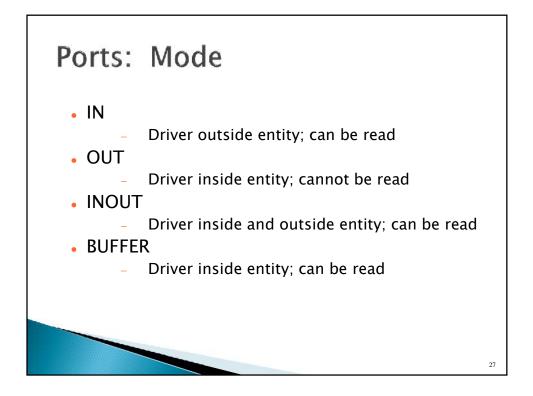

### Port Modes - Summary

The *Port Mode* of the interface describes the direction in which data travels with respect to the *component*

**In**: Data comes into this port and can only be read within the entity. It can appear **only on the right side** of a signal or variable assignment.

**Out**: The value of an output port can only be updated within the entity. **It cannot be read**. It can only appear **on the left side** of a signal assignment.

**Inout**: The value of a bi-directional port can be read and updated within the entity model. It can appear on **both sides** of a signal assignment.

28

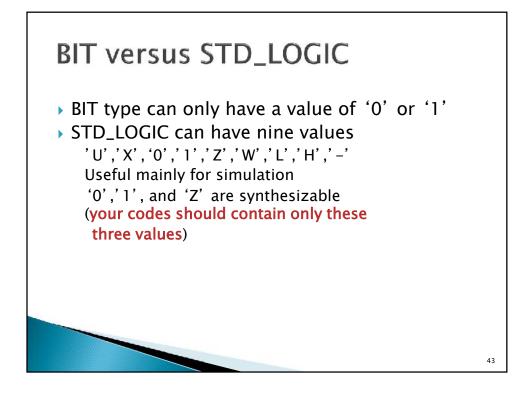

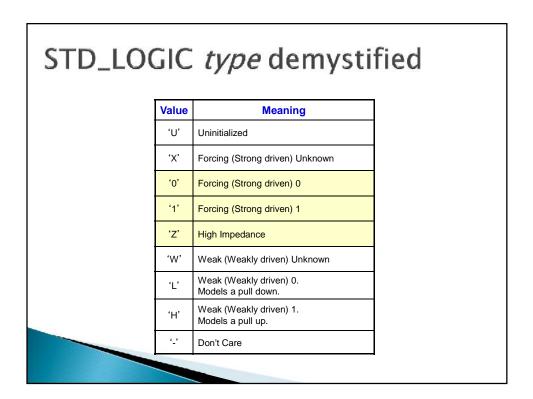

# Ports: Data Types

bit boolean integer natural positive character std\_ulogic std\_logic bit\_vector string std\_ulogic\_vector std\_logic\_vector

29

There are other data types, including enumerated types.

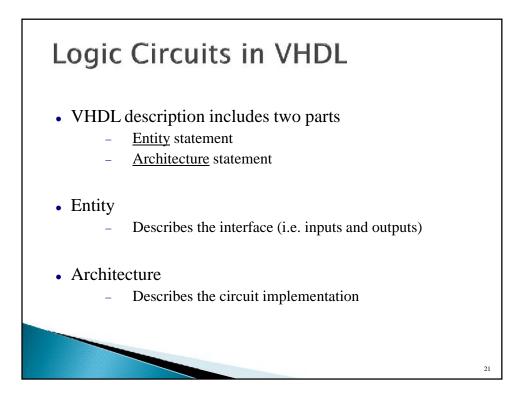

# **The Architecture Statement**Keyword: Architecture Requires a name The model is typically chosen as the name References the name of the associated Entity Specifies the functionality of the Entity Using one of several models Multiple architectures can be associated with a single entity. Only one architecture may be referenced

### The Architecture Statement

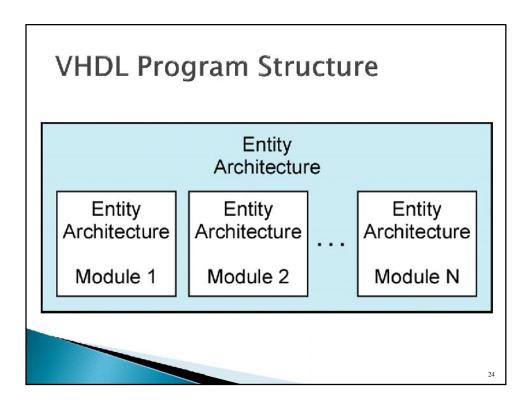

Associated with each entity is <u>one or more</u> architecture declarations of the form

architecture architecture-name of entity-name is

[declarations]

begin

architecture body end [architecture] [architecture-name];

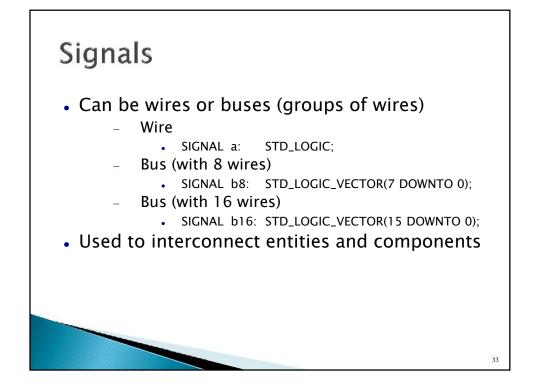

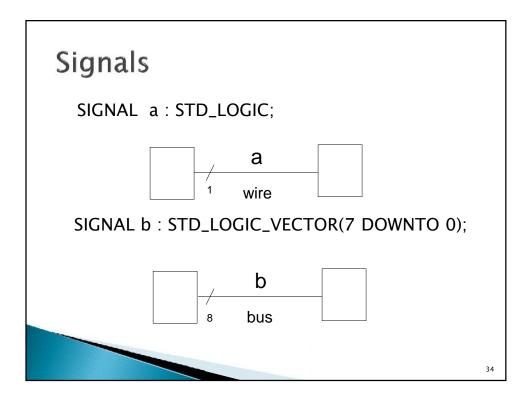

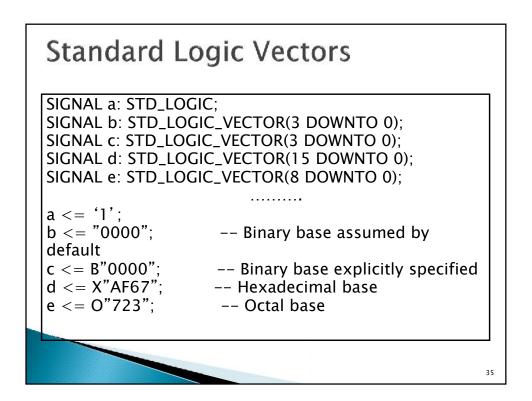

In the declarations section, we can declare signals and components that are used within the architecture. The architecture body contains statements that describe the operation of the module.

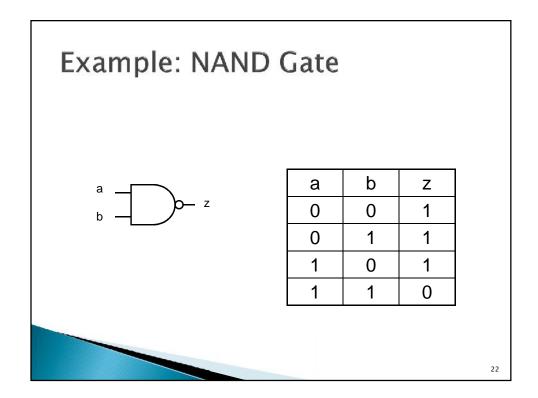

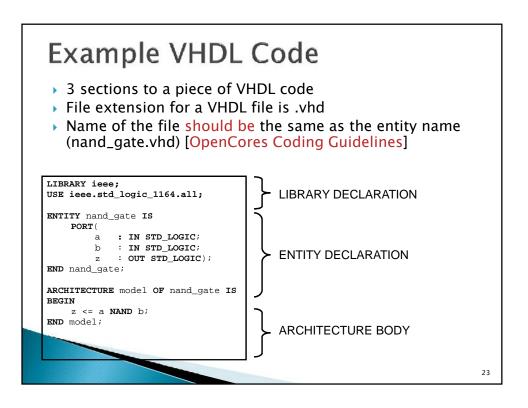

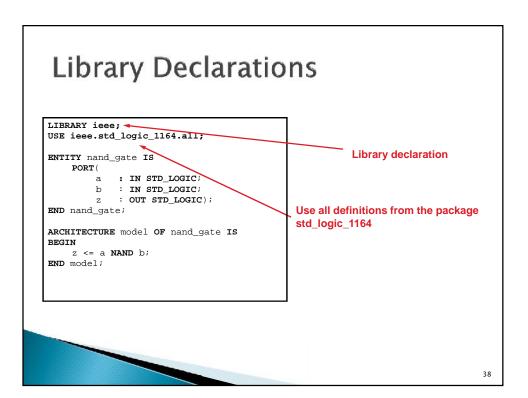

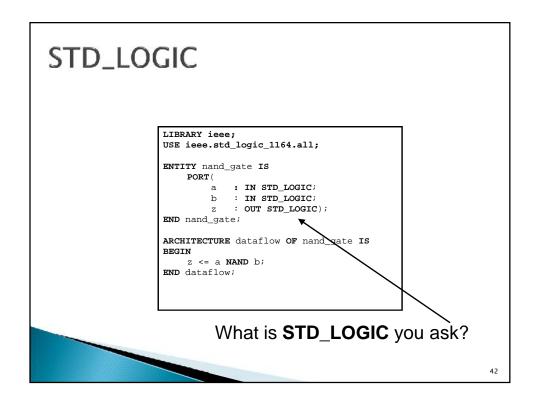

| Entity Declaration & Architecture |                                                                                                                                                                                                                                                                                |    |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| nand_gate.v                       | /hd                                                                                                                                                                                                                                                                            |    |  |

|                                   | <pre>LIBRARY ieee;<br/>USE ieee.std_logic_1164.all;<br/>ENTITY nand_gate IS<br/>PORT(<br/>a : IN STD_LOGIC;<br/>b : IN STD_LOGIC;<br/>z : OUT STD_LOGIC);<br/>END nand_gate;<br/>ARCHITECTURE dataflow OF nand_gate IS<br/>BEGIN<br/>z &lt;= a NAND b;<br/>END dataflow;</pre> |    |  |

|                                   |                                                                                                                                                                                                                                                                                | 32 |  |

37

### **VHDL** Operators

Predefined VHDL operators can be grouped into seven classes:

- 1. binary logical operators: and or nand nor xor xnor

- 2. relational operators: = /= < <= > >=

- 3. shift operators: sll srl sla sra rol ror

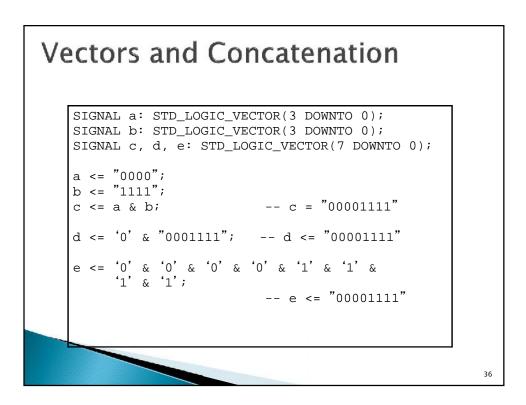

- 4. adding operators: + & (concatenation)

- 5. unary sign operators: + -

- 6. multiplying operators: \* / mod rem

- 7. miscellaneous operators: not abs \*\*

When parentheses are not used, operators in class 7 have the highest precedence and are applied first, followed by class 6, then class 5, etc.

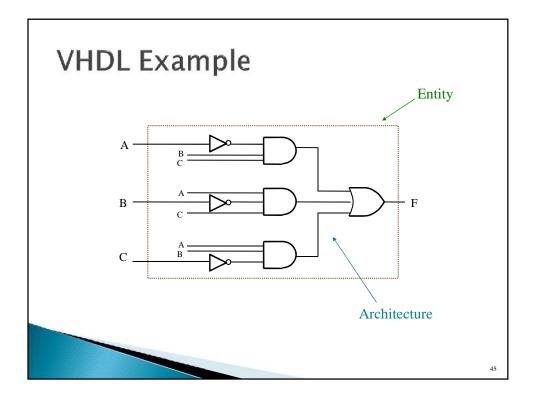

### VHDL Example 20 library IEEE; use IEEE.STD\_LOGIC\_1164.ALL; -- Uncomment the following library declaration if using -- arithmetic functions with Signed or Unsigned values 26 27 --use IEEE.NUMERIC\_STD.ALL; -- Uncomment the following library declaration if instantiating -- any Xilinx primitives in this code. --library UNISIM; --use UNISIM.VComponents.all; 30 entity comb\_logic\_ckt\_1 is Port ( A,B,C : in STD\_LCGIC; F : out STD\_LOGIC); 33 36 end comb\_logic\_ckt\_1; architecture Boolean\_Exp of comb\_logic\_ckt\_1 is 39 begin $F \le ( not(A) and B and C )$ or ( A and not(B) and C ) or ( A and B and not(C) ); end Boolean\_Exp;

| xor2     |                                                                                                         |    |

|----------|---------------------------------------------------------------------------------------------------------|----|

| xor2.vhd |                                                                                                         |    |

|          | LIBRARY ieee;<br>USE ieee.std_logic_1164.all;                                                           |    |

|          | ENTITY xor2 IS<br>PORT(<br>I1 : IN STD_LOGIC;<br>I2 : IN STD_LOGIC;<br>Y : OUT STD_LOGIC);<br>END xor2; |    |

|          | <pre>ARCHITECTURE dataflow OF xor2 IS BEGIN     Y &lt;= I1 xor I2; END dataflow;</pre>                  |    |

|          |                                                                                                         | 54 |

55

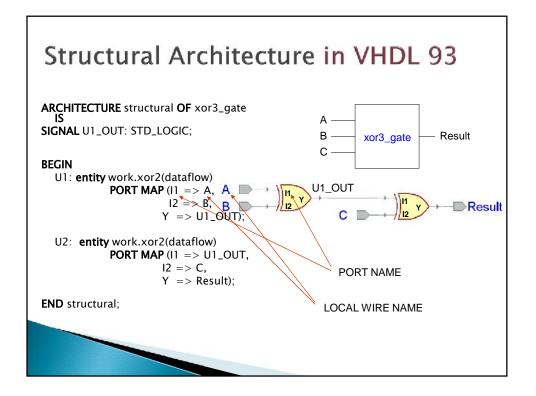

### **Structural Description**

- Structural design is the simplest to understand. This style is the closest to schematic capture and utilizes simple building blocks to compose logic functions.

- Components are interconnected in a hierarchical manner.

- Structural descriptions may connect simple gates or complex, abstract components.

- Structural style is useful when expressing a design that is naturally composed of sub-blocks.

- It accurately models what happens on the inputs and outputs of the black box (no matter what is inside and how it works).

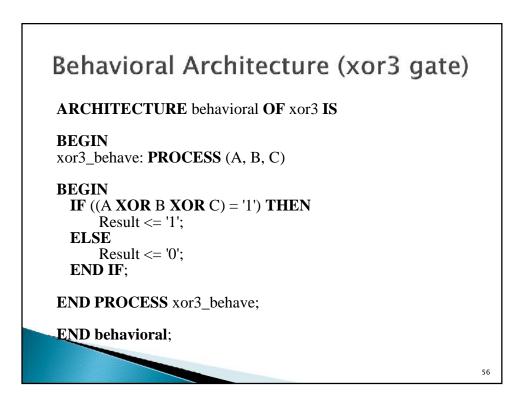

- > This style uses PROCESS statements in VHDL.