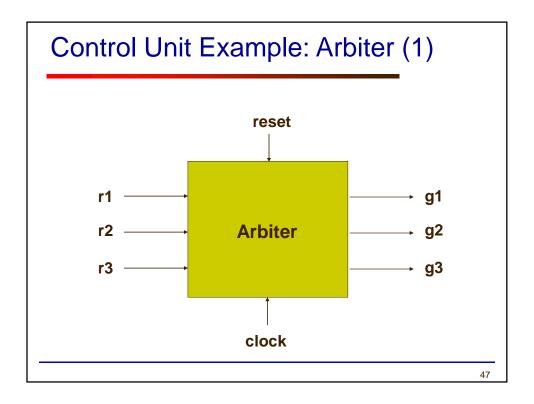

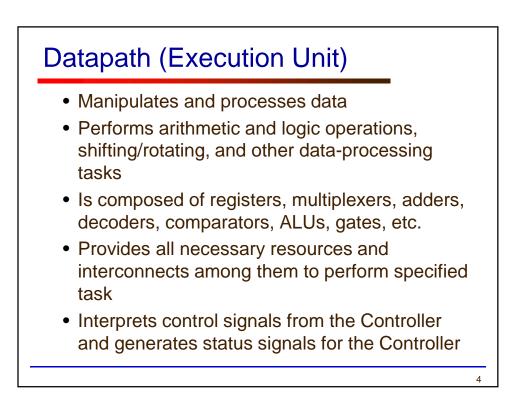

## Controller (Control Unit)

Controls data movements in the Datapath by switching multiplexers and enabling or disabling resources

> Example: enable signals for registers Example: select signals for muxes

- Provides signals to activate various processing tasks in the Datapath

- Determines the sequence of operations performed by the Datapath

- Follows Some 'Program' or Schedule

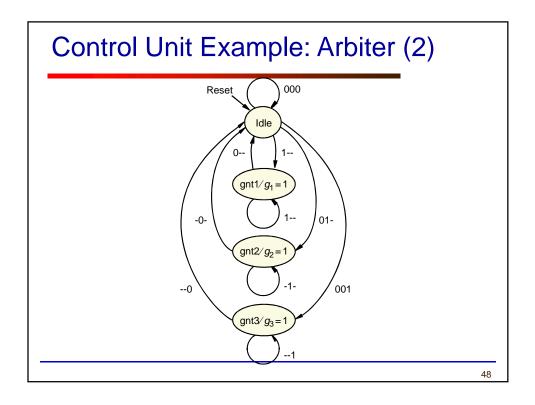

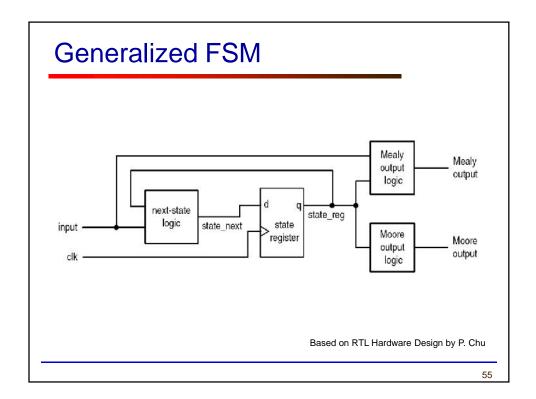

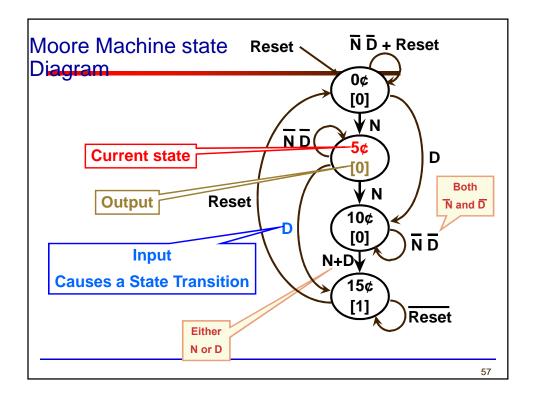

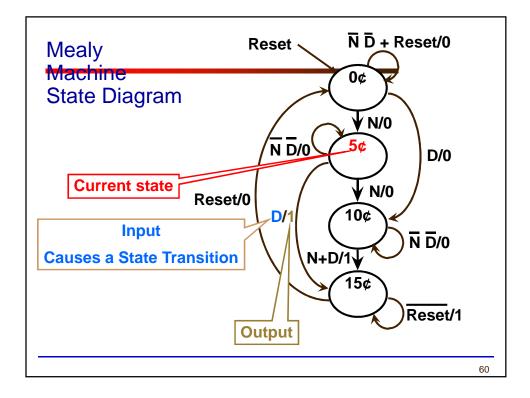

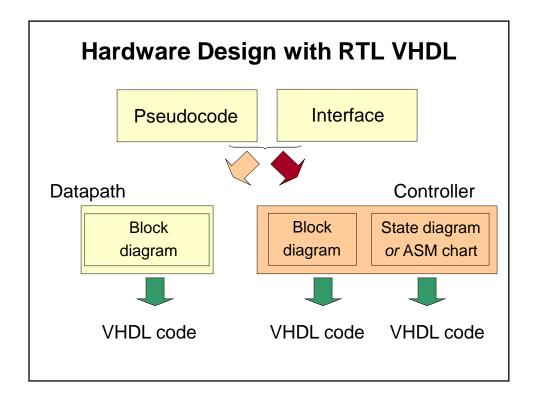

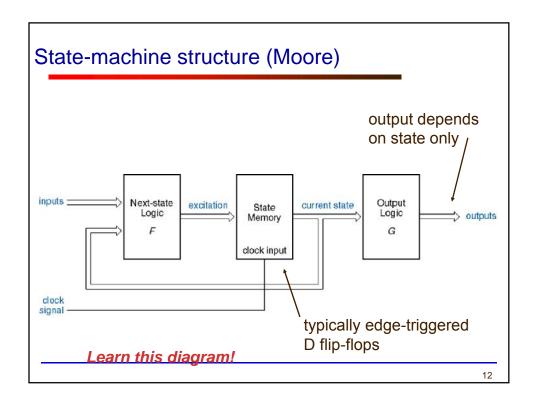

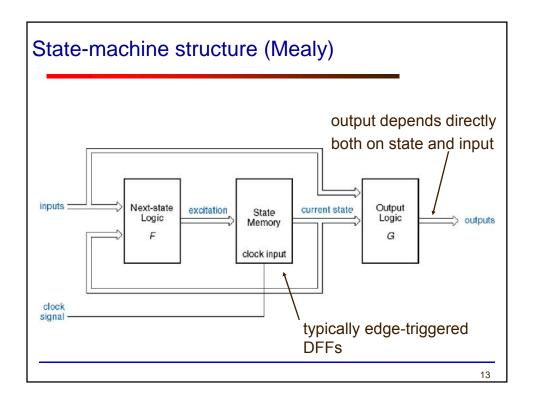

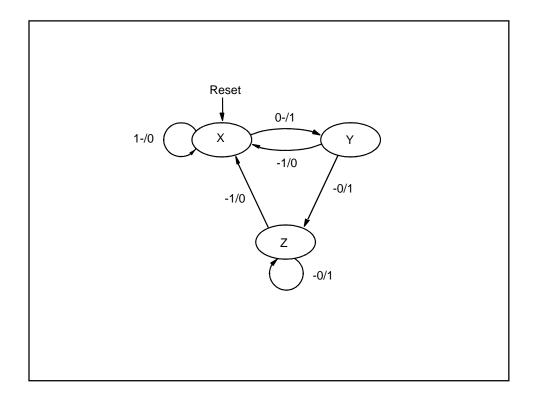

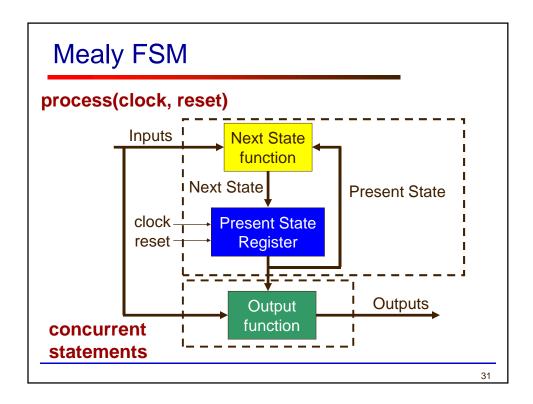

- Digital Systems and especially their Controllers can be described as Finite State Machines (FSMs)

- Finite State Machines can be represented using

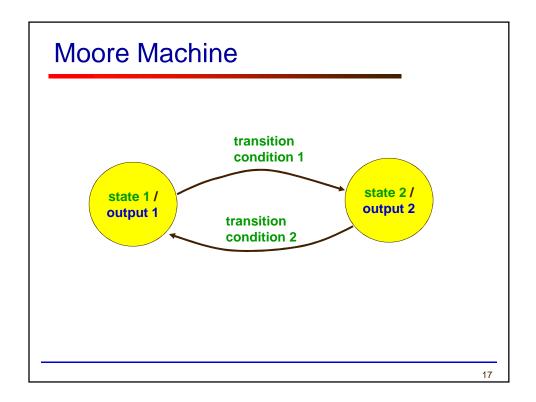

- State Diagrams and State Tables suitable for simple digital systems with a relatively few inputs and outputs

- Algorithmic State Machine (ASM) Charts suitable for complex digital systems with a large number of inputs and outputs

- All these descriptions can be easily translated to the corresponding synthesizable VHDL code

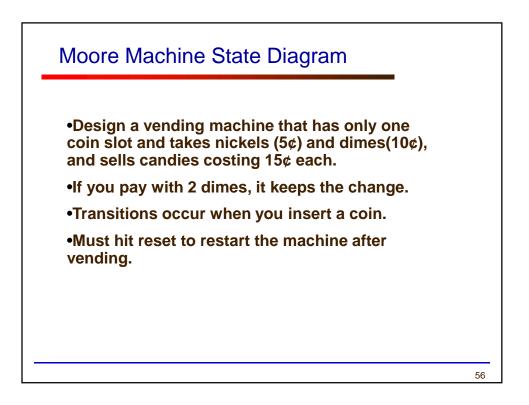

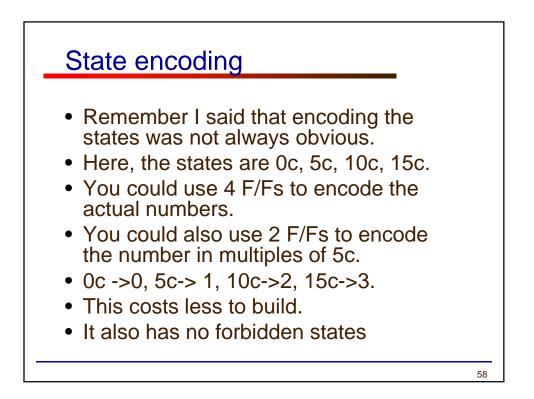

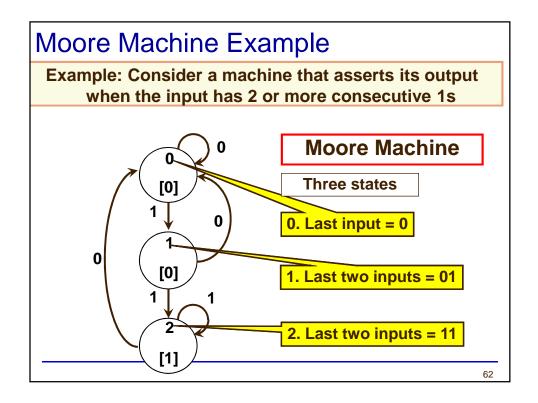

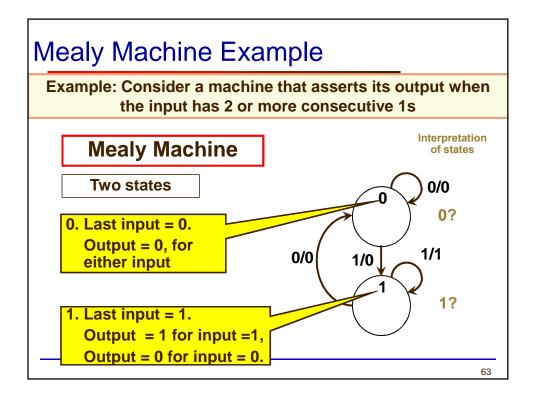

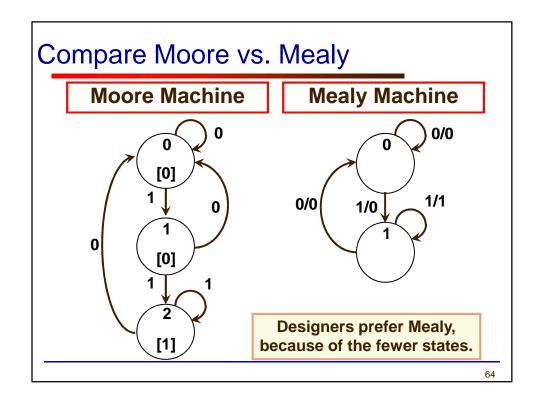

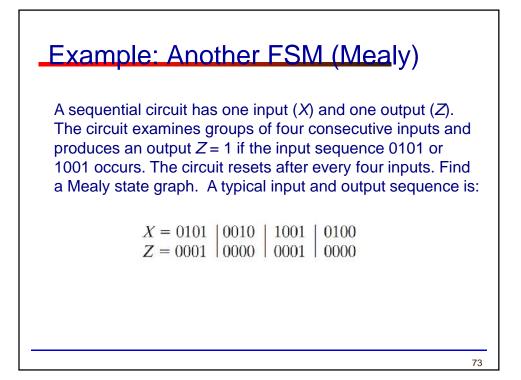

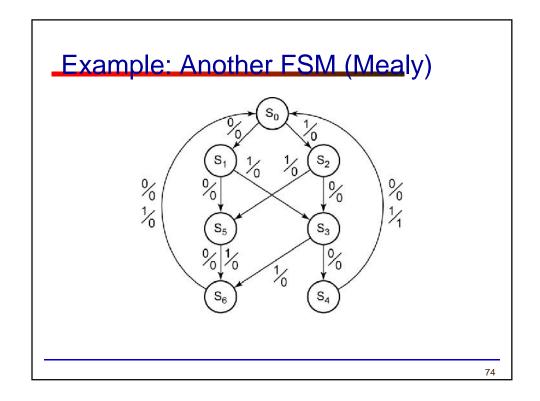

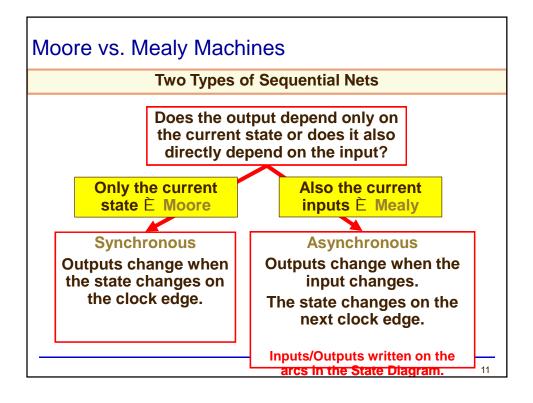

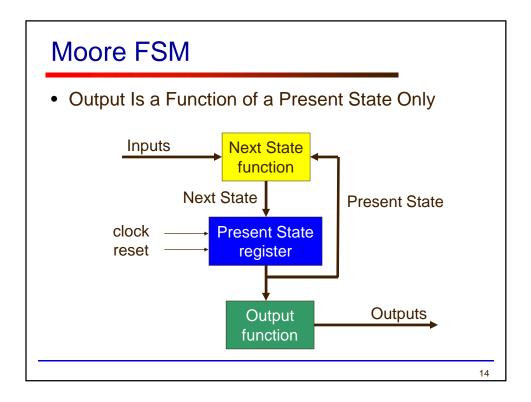

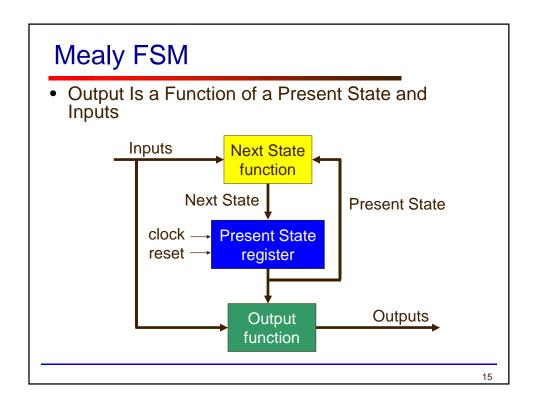

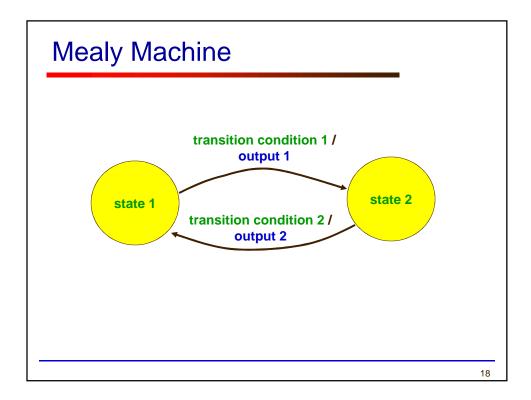

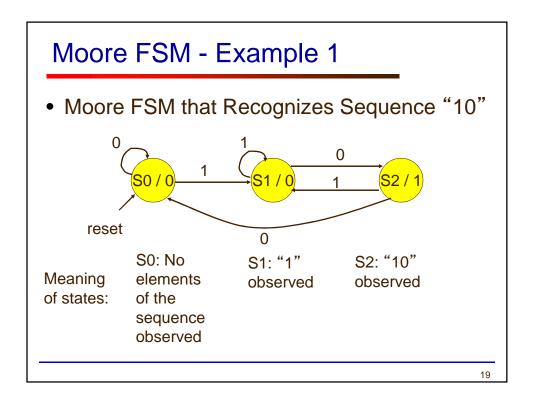

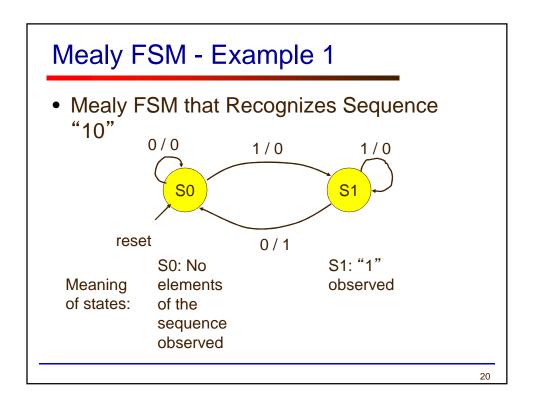

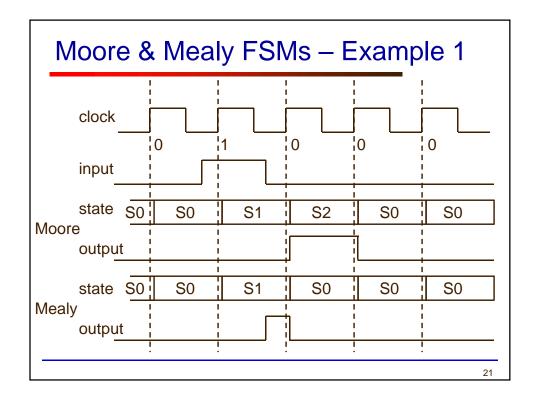

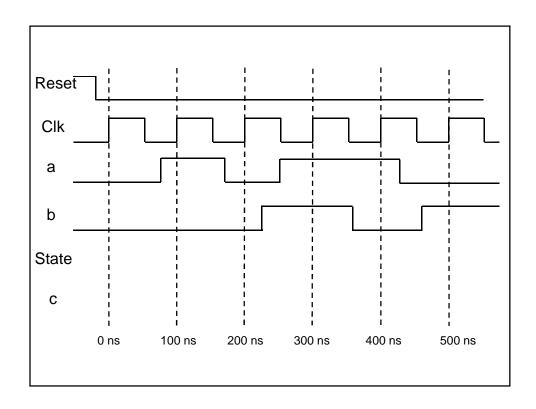

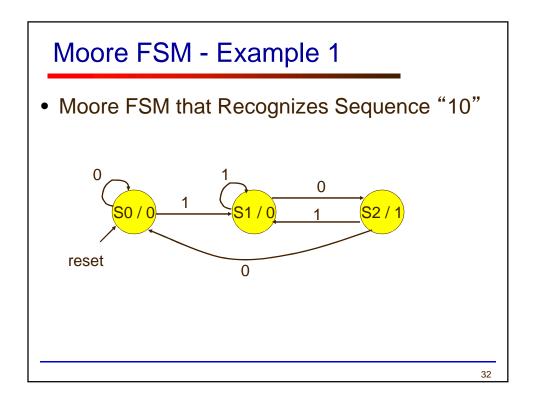

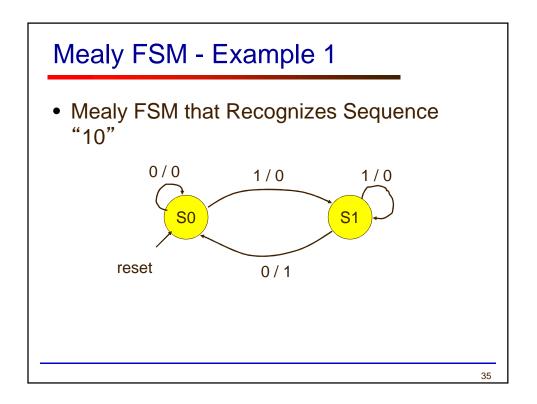

## Finite State Machines (FSMs) An FSM is used to model a system that transits among a finite number of internal states. The transitions depend on the current state and external input. The main application of an FSM is to act as the controller of a medium to large digital system Design of FSMs involves Defining states Defining next state and output functions Optimization / minimization Manual optimization/minimization is practical for small FSMs only

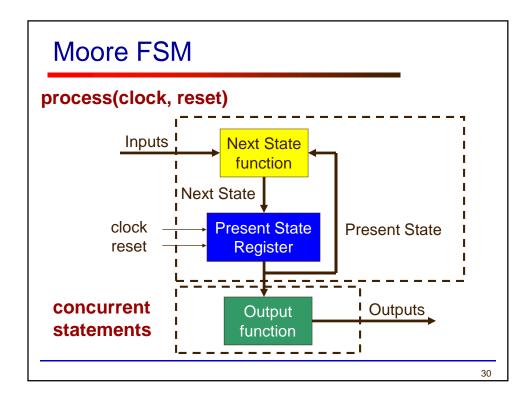

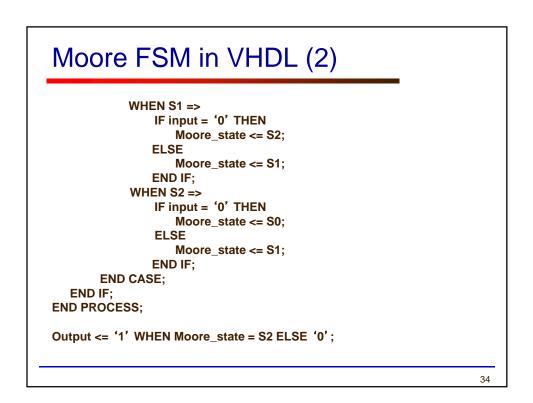

## Moore FSM in VHDL (1)

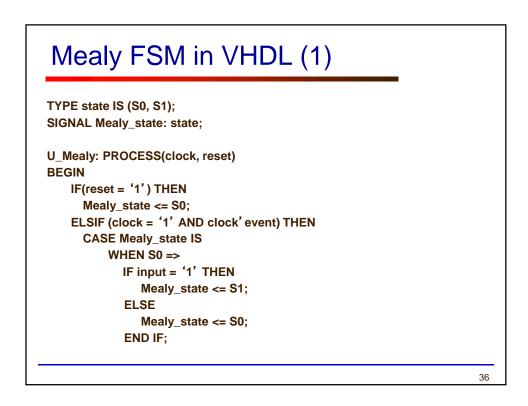

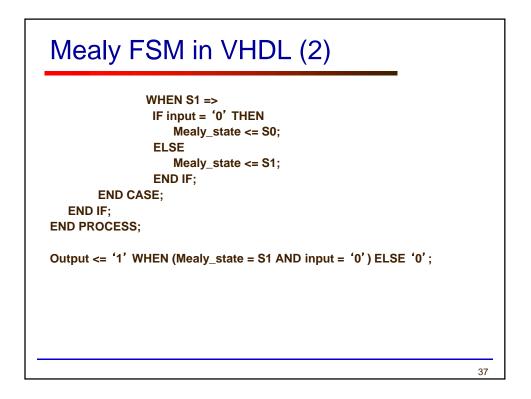

TYPE state IS (S0, S1, S2); SIGNAL Moore\_state: state;

U\_Moore: PROCESS (clock, reset) BEGIN IF(reset = '1') THEN Moore\_state <= S0; ELSIF (clock = '1' AND clock' event) THEN CASE Moore\_state IS WHEN S0 => IF input = '1' THEN Moore\_state <= S1; ELSE Moore\_state <= S0; END IF;

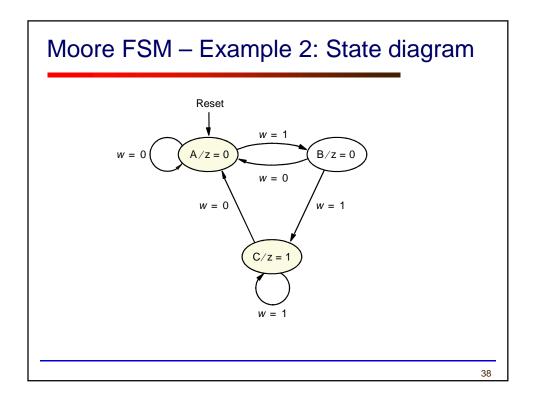

## Moore FSM – Example 2: State table

| Present | Next state |              | Output |

|---------|------------|--------------|--------|

| state   | w = 0      | <i>w</i> = 1 | Z      |

| А       | А          | В            | 0      |

| В       | А          | С            | 0      |

| С       | А          | С            | 1      |

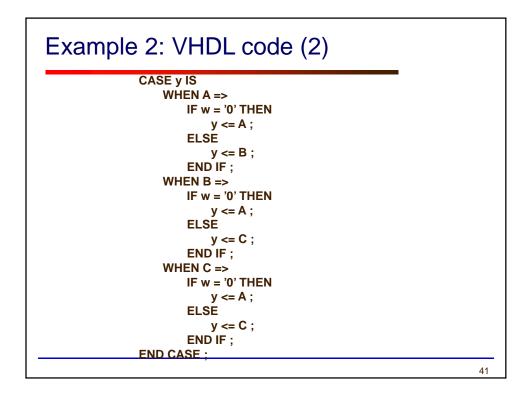

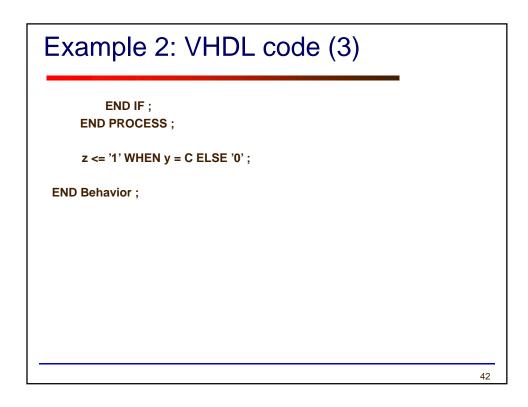

| Example 2: VHDL code (1)                                                                                                                    |   |

|---------------------------------------------------------------------------------------------------------------------------------------------|---|

| USE ieee.std_logic_1164.all ;                                                                                                               |   |

| ENTITY simple IS<br>PORT ( clock : IN STD_LOGIC ;<br>resetn : IN STD_LOGIC ;<br>w : IN STD_LOGIC ;<br>z : OUT STD_LOGIC ) ;<br>END simple ; |   |

| ARCHITECTURE Behavior OF simple IS<br>TYPE State_type IS (A, B, C) ;                                                                        |   |

| SIGNAL y : State_type ;<br>BEGIN<br>PROCESS ( resetn, clock )<br>BEGIN                                                                      |   |

| IF resetn = '0' THEN<br>y <= A ;<br>ELSIF (Clock'EVENT AND Clock = '1') THEN                                                                |   |

|                                                                                                                                             | 4 |

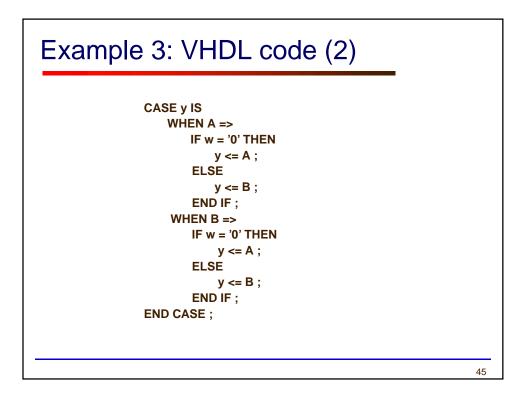

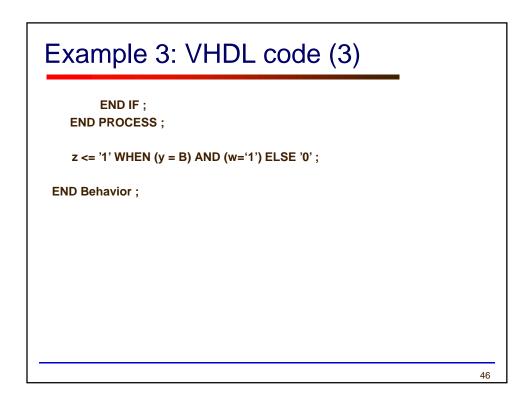

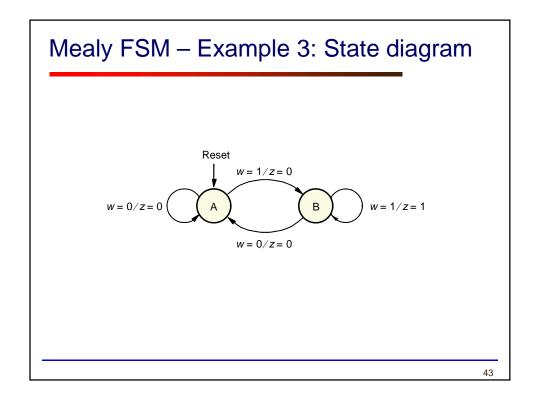

| Example 3: VHDL code (1)                                                                                                                   |    |

|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| LIBRARY ieee ;<br>USE ieee.std_logic_1164.all ;                                                                                            |    |

| ENTITY Mealy IS<br>PORT ( clock : IN STD_LOGIC ;<br>resetn : IN STD_LOGIC ;<br>w : IN STD_LOGIC ;<br>z : OUT STD_LOGIC ) ;<br>END Mealy ;  |    |

| ARCHITECTURE Behavior OF Mealy IS<br>TYPE State_type IS (A, B) ;<br>SIGNAL y : State_type ;<br>BEGIN<br>PROCESS ( resetn, clock )<br>BEGIN |    |

| IF resetn = '0' THEN<br>y <= A ;<br>ELSIF (clock'EVENT AND clock = '1') THEN                                                               |    |

|                                                                                                                                            | 44 |